# **Unidad Ejecutora:**

## DEPARTAMENTO DE INGENIERÍA E INVESTIGACIONES TECNOLÓGICAS

# Título del proyecto de investigación:

Desarrollo de plataformas educativas para la enseñanza de Sistemas Embebidos

# Código del proyecto:

C2-ING-026

# Programa de acreditación:

CyTMA2

# **Director del proyecto:**

Pérez, Alejandro Sigfrido

# **Co-Director del proyecto:**

Zaradnik, Ignacio José

# Integrantes del equipo:

Tantignone, Hugo; Brengi, Diego; Garcia, Gerardo; Cipollone Federico; Vaca Gonzalo.

## Fecha de inicio:

01/01/2015

### Fecha de finalización:

31/12/2016

**Informe Final**

#### Sumario

| 1. | Resumen             | p.nº2  |

|----|---------------------|--------|

| 2. | Memoria descriptiva | p.nº3  |

| 3. | Introducción'       | p.nº7  |

| 4. | Desarrollo          | p.nº10 |

| 5. | Conclusiones        | p.nº40 |

| 6. | Bibliografía        | p.nº41 |

| 7  | Anexas              | n nº42 |

#### 1. Resumen

Los avances en las Tecnologías de la Información y Comunicación (TIC), así como el desarrollo de nuevo dispositivos electrónicos, microcontroladores, microporcesadores, memorias, fuentes de alimentación, sensores, transmisores y receptores de radiofrecuencia, etc, ha llevado a un aumento de la complejidad de los equipos electrónicos. Por lo tanto, un buen diseño del sistema embebido incluido en el equipo, permitirá que los dispositivos puedan cumplir eficientemente su función y que el proceso de manufactura asociado a ellos sea más rápido y eficiente. Como ejemplo de esto se pueden citar los siguientes ejemplos:

- La familiarización con teléfonos celulares y tabletas a llevado a que productos industriales incluyan interfaces Hombre maquinas más sofisticadas y semejantes a los dispositivos nombrados.

- La necesidad de Robustez en las aplicaciones Industriales ha llevado al desarrollo de sistemas operativos de tiempo Real (RTOS), en los cuales existe un control de entradas y salidas en donde se establecen en consecuencia todos "procesos" en fracciones de tiempo exacto.

- La búsqueda del aumento de la eficiencia de dispositivos electromecánicos implica la inclusión de un sistema de monitoreo y control, en el cual las funciones del sistema embebido son fundamentales.

Es por este motivo que es de vital importancia el diseño de una plataforma de enseñanza de sistemas embebidos, que permitirá la formación de profesionales con conocimiento y experiencia en los sistemas embebidos, los cuales se podrán desarrollar en diversas áreas de la industria electrónica local.

Palabras claves: Circuitos impresos, Sistemas Embebidos, Computadora Industrial Argentina Abierta, Impedancia controlada

2

## 2. Memoria descriptiva

# 2.1- Estado de investigación

Los objetivos del proyecto se lograron cumplir casi en su totalidad. Sin embargo el cronograma de tareas replanteado para el 2016 se cumplió parcialmente. Las principales causas de esto son: la falta de coordinación entre los distintos grupos de trabajo involucrados (ACSE, INTI, UNLaM), la asignación de fondos y la disponibilidad en forma local de componentes. En la sección 2.2.3 se detallar consecuencias de ellas.

Con el fin de aprovechar el tiempo se realizaron otras tareas, como ser el diseño de ponchos modelo y el comienzo de un desarrollo, dentro del marco del proyecto CIAA, para la empresa Equiser.

A pesar de esto se considera que los objetivos planteados han sido cumplidos, lo cual será detallado en las conclusiones.

## 2.2- Evaluación del equipo y presupuesto.

El equipo de trabajo se desempeño en forma correcta, cumpliendo los plazos de tiempos estipulados al organizar las tareas e intentado utilizar el tiempo asignado en tareas asociadas al proyecto, mientras no se podía avanzar con las estructuradas.

En lo referente al presupuesto, la primera cuota de los fondos asignados fue depositada avanzado el 2016, mientras que la segunda aun no fue asignada. Previendo estos inconvenientes se articularon métodos que permitirón continuar sin presupuesto, pero como se detallará a continuación esto ocasionó grandes demoras de tiempo. Aprovechando la articulación realizada, los fondos asignados fueron empleados para equipamiento, el cual tiene por objetivo el montaje de los prototipos desarrollados.

#### 2.3- Cronograma de actividades

Tal como se comento, el cronograma de previsto se cumplió parcialmente. Las tareas de estudio y diseño del Poncho Ethernet fueron desarrolladas en tiempo y forma, así como el estudio de equipamiento. Los problemas surgieron al momento de fabricación de los circuitos impresos de la CIAA-FSL y del Poncho Ethernet.

Al finalizar el 2015, la placa CIAA-FSL se encontraba en revisión por el INTI, quienes presentaron para fines de febrero un informe sobre su evaluación y sugerencias de mejora, disponibles en el siguiente link:

https://github.com/ciaa/Hardware/blob/master/PCB/EDU-FSL/EDU\_CIAA\_K60/doc/revision1/EDU-CIAA-FSL\_Rev.pdf

Recibido este, quedo en manos del responsable de las versiones educativas, y a la fecha no se ha tenido novedad. Para la fabricación del circuito impreso se dispone de un Voucher donado por Circuitos impresos Mayer, mientras que para los componentes se estaba en tratativas con Electrocomponentes S.A. el armado se efectuaría en las instalaciones de la UNLaM.

En lo que respecta al circuito impreso del poncho Ethernet, al no contar con fondos, se demoró la fabricación hasta el momento que se consiguió la fabricación del mismo con fondos del ACSE, los componentes del mismo serán provistos por Electrocomponentes S.A. quien en este momento está en tratativas para importarlos.

Consecuentemente la puesta en marcha, la documentación y la transferencia de estas placas esta demorada.

#### 2.4- Transferencias

#### 2.4.1- Periodo 2015

"Adaptación de un dispositivo USB de entrada táctil para el ordenador pensando en su aplicación en terapia ocupacional" VIII Congreso Iberoamericano de Tecnologías de Apoyo a la Discapacidad (Iberdiscap 2015) ISBN: 978-956-9763-00-7

Dictado de la presentación "Resumen de conceptos generales sobre diseño de circuitos impresos" en el marco del curso teórico – práctico sobre "Introducción al Uso de KiCad para el diseño de Circuitos Impresos de Mediana Complejidad y Multicapa" dictado por el INTI.

#### 2.4.2- Periodo 2016

Tal como se ha hecho referencia, la demora en la fabricación y puesta en marcha de las placas desarrolladas ha impedido la presentación de trabajos asociadas a las mismas.

Por tratarse de un proyecto de hardware libre, los diseños están disponibles para ser utilizados por cualquier interesado bajo una licencia BSD. A continuación se detallan los links a un repositorio con el trabajo realizado

https://github.com/ciaa/Hardware/tree/master/PCB/EDU-FSL https://github.com/ciaa/Ponchos/tree/master/ethernet\_LAN8720A\_v2 https://github.com/ciaa/Ponchos/tree/master/modelos https://github.com/ciaa/Hardware/tree/master/PCB/FSL-MINI

#### 3. Introducción

#### 3.1. Selección del Tema

La selección del tema, "Desarrollo de plataformas educativas para la enseñanza de Sistemas Embebidos", se fundamenta en la importancia que día a día están tomando los sistemas electrónicos y en especial los sistemas embebidos en nuestras vidas. En el Resumen del proyecto, previamente presentado, se ejemplifican algunos de estos casos, siendo también un sistema embebido el corazón de cualquier dispositivo IoT (Internet de las Cosas).

Esta importancia se ve ejemplificada en las distintas instituciones y asociaciones, tanto a nivel internacional como local, que se ocupan de estos temas. Entra ellas encontramos la Organización Internacional del Trabajo (OIT), la IPC Association Connecting Electronics Industries, la Asociación Civil para la Investigación, Promoción y Desarrollo de los Sistemas Embebidos (ACSE) y la Cámara Argentina de Industrias Electrónicas, Electromecánicas y Luminotécnicas (CADIEEL)[1][2][3][4]. En el Anexo II, "La industria Electrónica", se profundiza sobre este punto.

#### 3.2. Definición del Problema

Los avances en las Tecnologías de la Información y Comunicación (TIC), así como el desarrollo de nuevo dispositivos electrónicos, microcontroladores, microporcesadores, memorias, fuentes de alimentación, sensores, transmisores y receptores de radiofrecuencia, etc., ha llevado a un aumento de la complejidad y de la funcionalidades de los equipos electrónicos, un ejemplo cotidiano de esto son los teléfonos celulares, pero como estos se pueden citar también equipos de electromedicina, controles para la industria, etc. Dichos equipos poseen un sistema electrónico que esta contenido ("embebido") dentro de ellos, así como también partes mecánicas, electromecánicas, etc. El mismo realiza un procesamiento de datos, pero que, a diferencia de una computadora personal, está diseñado para satisfacer una función específica. Sistemas embebidos es el nombre genérico que reciben dichos sistemas electrónicos.

Para el desarrollo de estos sistemas embebidos es necesario contar con un conjunto de herramientas, kit de desarrollo, programador/debugger y un ambiente de desarrollo integrado (IDE) entre los principales. Estas herramientas suelen ser de origen extranjero, teniendo su costo en dólares y actualmente una gran dificultad para importarse, lo que representa un problema para los estudiantes y desarrolladores locales.

### 3.3. Justificación del Estudio

El cerebro de un sistema embebido es típicamente un microcontrolador, aunque los datos también pueden ser procesados por un DSP, una FPGA, un microprocesador o un ASIC, y su diseño está optimizado para reducir su tamaño y su costo, aumentar su confiabilidad y mejorar su desempeño. Algunas aplicaciones también tienen requisitos de bajo consumo, como por ejemplo un celular o un reproductor de MP3, que se satisfacen gracias a los avances en la tecnología.

Por lo tanto, un buen diseño del sistema embebido incluido en el equipo, permitirá que los dispositivos puedan cumplir eficientemente su función y que el proceso de manufactura asociado a ellos sea más rápido y eficiente. Como ejemplo de esto se pueden citar los siguientes:

- La familiarización con teléfonos celulares y tabletas a llevado a que productos industriales incluyan interfaces Hombre maquinas más sofisticadas y semejantes a los dispositivos nombrados.

- La necesidad de Robustez en las aplicaciones Industriales ha llevado al desarrollo de sistemas operativos de tiempo Real (RTOS), en los cuales existe un control de entradas y

- salidas en donde se establecen en consecuencia todos "procesos" en fracciones de tiempo exacto.

- La búsqueda del aumento de la eficiencia de dispositivos electromecánicos implica la inclusión de un sistema de monitoreo y control, en el cual las funciones del sistema embebido son fundamentales.

Es por este motivo que es de vital importancia el diseño de una plataforma de enseñanza de sistemas embebidos, que permitirá la formación de profesionales con conocimiento y experiencia en los sistemas embebidos, los cuales se podrán desarrollar en diversas áreas de la industria electrónica local.

#### 3.4. Limitaciones

Como limitaciones para el desarrollo de este proyecto nos encontramos con los siguientes temas:

- Disponibilidad de un software de diseño de circuitos impresos de uso estandarizado en la carrera de Ingeniería Electrónica.

- Capacidad limitada de los fabricantes locales de circuitos impresos.

- Heterogeneidad de conocimientos en los miembros del grupo.

- Disponibilidad de recursos económicos.

## 3.5. Hipótesis

Como Hipótesis del proyecto se pueden resumir lo planteado en la definición del problema y la justificación del estudio, ambos presentados previamente.

Los avances en las Tecnologías de la Información y Comunicación (TIC), así como el desarrollo de nuevo dispositivos electrónicos, microcontroladores, microporcesadores, memorias, fuentes de alimentación, sensores, transmisores y receptores de radiofrecuencia, etc, ha llevado a un aumento de la complejidad de los equipos electrónicos. Por lo tanto, un buen diseño del sistema embebido incluido en el equipo, permitirá que los dispositivos puedan cumplir eficientemente su función y que el proceso de manufactura asociado a ellos sea más rápido y eficiente. Como ejemplo de esto se pueden citar los siguientes ejemplos:

- La familiarización con teléfonos celulares y tablets a llevado a que productos industriales incluyan interfaces Hombre maquinas más sofisticadas y semejantes a los dispositivos nombrados.

- La necesidad de Robustez en las aplicaciones Industriales a llevado al desarrollo de sistemas operativos de tiempo Real (RTOS), en los cuales existe un control de entradas y salidas en donde se establecen en consecuencia todos "procesos" en fracciones de tiempo exacto.

- La búsqueda del aumento de la eficiencia de dispositivos electromecánicos implica la inclusión de un sistema de monitoreo y control, en el cual las funciones del sistema embebido son fundamentales.

Es por este motivo que es de vital importancia el diseño de una plataforma de enseñanza de sistemas embebidos, que permitirá la formación de profesionales con conocimiento y experiencia en los sistemas embebidos, los cuales se podrán desarrollar en diversas áreas de la industria electrónica local.

#### 3.6. Objetivos

El proyecto tiene como objetivos:

La elaboración de una placa de desarrollo para la enseñanza de sistemas emebebidos, la cual se encuadernara en el marco del proyecto CIAA (<a href="http://www.proyecto-ciaa.com.ar/devwiki/doku.php">http://www.proyecto-ciaa.com.ar/devwiki/doku.php</a>), así como también algunas placas auxiliares para la antes mencionada.

La formación de recursos humanos en el diseño y manufactura de placas de circuitos impresos, de forma de poder realizar asesoramiento a pequeñas y medianas empresas del rubro electrónico en la actualización de sus diseños y el desarrollo de nuevos productos con nuevas tecnologías. Desde diseños que incluyan componentes de montaje superficial de dos o mas capas con buses de alta velocidad.

Otro objetivo buscado es brindar a los alumnos de la carrera de Ingeniería Electrónica un lugar donde puedan adquirir conocimientos extracurriculares de gran importancia para su inserción en el mercado actual.

## 3.7. Alcances del Trabajo

Los alcances de proyecto se resumen en los siguientes puntos:

- Diseño y fabricación de circuitos impresos simple faz con tecnología mixta (PTH y SMD) utilizando técnicas caseras.

- Diseño de una plataforma educativas para la enseñanza de Sistemas Embebidos encuadrada en el marco del proyecto CIAA. La cual será un diseño de doble faz, en el cual se tendrán en cuenta consideración de líneas de impedancia controlada y se fabricara en un proveedor local.

- Diseño de un o mas placas auxiliares para la plataforma educativa desarrollada, teniendo en cuenta las mismas especificaciones tenidas en esta.

En el Anexo III, se realiza una breve descripción del proyecto CIAA.

#### 4. Desarrollo

## 4.1. Material y Métodos

Para llevar adelante el proyecto se requirió de los siguientes materiales:

- Computadora Personal.

- Software de diseño de circuitos impresos.

- Placas vírgenes para la fabricación de impresos.

- Materiales químicos para la fabricación de los circuitos impresos.

- Accesorios varios para la fabricación de los circuitos impresos.

- Componentes electrónicos varios.

- Equipamiento para soldado de componentes.

Por no contar con el presupuesto asignado, se trabajo con una computadora personal perteneciente al grupo de inteligencia ambiental y se emplearon materiales pertenecientes al Laboratorio Abierto de la Carrera de Ingeniería Electrónica.

El software de diseño de circuito impreso utilizado fue el Kicad, el cual es de libre distribución. En el Anexo IV se presenta el estudio realizado para la selección del mismo.

Como se detallará a continuación, se fabricaron a algunos circuitos impresos de simple faz. Para dicha fabricación se empleo el método casero, el cual consta de los siguientes pasos:

- Preparación de la superficie de la placa virgen.

- Impresión de nuestro diseño sobre papel que permita la transferencia con impresora laser.

- Transferencia del diseño a través de calor (plancha).

- Colocación de la placa con diseño transferido en acido para la generación del impreso.

- Extracción, limpieza, inspección y corrección de posibles fallas.

- Aplicación de productos guímicos para evitar el oxidamiento de la superficie.

## 4.2. Lugar y Tiempo de la Investigación

La investigación fue llevada a cabo en el Laboratorio Abierto de la Carrera de Ingeniería Electrónica, el cual es parte del Laboratorio de Electrónica del departamento de Ingeniería e Investigaciones Tecnológicas de la Universidad Nacional de la Matanza.

### 4.3. Descripción del Objeto de Estudio

Como objetos de estudio en esta etapa de la investigación se plantearon:

- Una contextualización de la industria electrónica, detallo en el Anexo 2, a fin de poder definir el contexto del trabajo a realizar.

- El proyecto CIAA, detallado en el Anexo 3, a fin de entender los objetivos y motivadores del proyecto, así como también como muestro trabajo puede ayudar a generar un crecimiento del proyecto.

- Los softwares de diseño de circuitos impresos, detallados en el Anexo 4, a través del cual se desarrollara la plataforma educativa.

- Reglas y consideraciones de diseño, las cuales serán tenidas en cuenta en el diseño y fabricación de la plataforma educativa.

## 4.4. Descripción de Población y Muestra

Al plantearse como parte de uno de los objetivos que la plataforma educativa desarrollada estuviera en el marco del proyecto CIAA, las consideraciones sobre población y muestra fueron realizadas por los miembros de la Asociación Civil para la Investigación, Promoción y Desarrollo de los Sistemas Embebidos (ACSE).

Pudiéndose considerar que se tomo como población el universo de las plataformas educativas, las cuales abarcan plataformas para microcontroladores, microprocesadores, procesadores digitales de señal y FPGA, teniendo para un mismo tipo de plataforma múltiples alternativas que varían en prestaciones y costo. Y considerándose como muestra las plataformas de microcontroladores de bajo costo.

## 4.5. Diseño de la Investigación

A raíz que el grupo se encuentra formado por participantes con distinto nivel de conocimiento y experiencia en el manejo de Kicad, especialmente el caso de los alumnos que forman parte del proyecto, se decidió comenzar con diseños sencillos para ir nivelando los conocimientos. Se plantearon los siguientes diseños:

- Modulo de Leds para Robots Sumo.

- Makey Makey.

- Modulo de Acelerómetro para Robots Sumo.

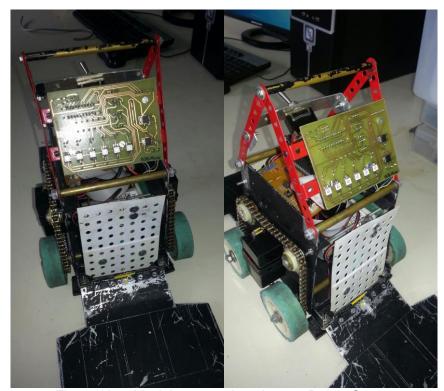

## 4.5.1- Modulo de Leds para Robots Sumo

Independiente del objetivo citado arriba, la idea de este circuito es agregar a los robots de sumo que participan en la competencia anual (Robolucha) una placa con varios LEDs RGB y diferentes efectos dependiendo de la acción o el estado del robot.

### 4.5.1.1- Reglas de diseño

A continuación se detallan las reglas y consideraciones que se debieron tomar en cuenta para el desarrollo de los módulos.

- Proceso de fabricación a través de transferencia térmica (plancha), soporte de pertinax, cloruro férrico, flux en aerosol y agujereado con Dremel (mechas de 0,8, 0,9, 1, 1,2 mm y superiores).

- Componentes thru hole salvo los diodos RGB que son del tipo SMD formato 50-50.

- Pistas iguales o mayores a 20 mils.

- Se debe buscar que los tamaños de agujeros estén normalizados (drill report) y se utilicen la menor cantidad de diámetros.

- El PCB debe ser simple faz y se debe usar la capa bottom.

- Se permiten algunos puentes, siempre los más cortos posibles y en posición horizontal o vertical (nunca en diagonal). Los puentes se implementan como si se ruteara en la capa 2 (Top).

- Los tamaños de vías deben ser similares a los tamaños de pads thru hole, ya que se fabrican y se sueldan por método manual.

- Dimensiones máximas 20x20 cm.

### 4.5.1.2- Esquemático

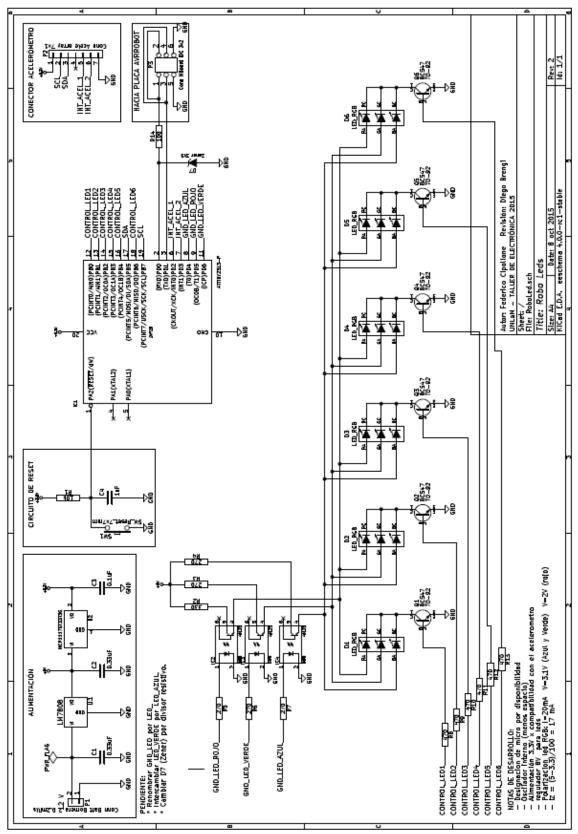

En la Figura N°1 se presenta el esquemático del modulo desarrollado.

## 4.5.1.3- Circuito impreso

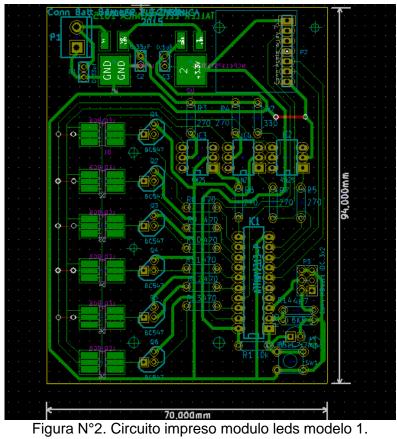

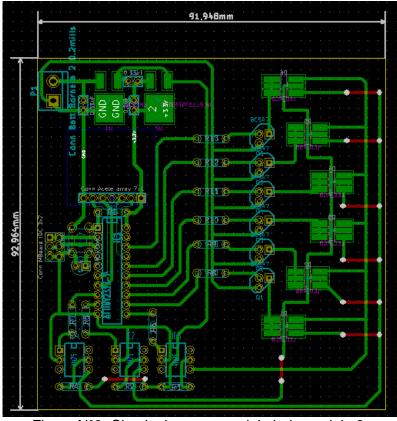

En la Figura N°2 y la Figura N°3 se presentan dos circuitos impresos de los módulos de leds.

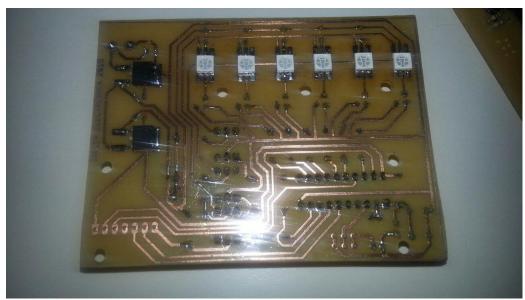

## 4.5.1.4- Fabricación y armado

La fabricación y el armado de dichos módulos se llevo a cabo en las instalaciones y con materiales del Laboratorio abierto de la carrera de Ingeniería Electrónica (Lacie). La Figura N°4 nos muestra el modulo armado y la Figura N°5 nos muestra el modulo montado sobre un Robot Sumo. El armado por tratarse en su mayoría de componentes thru hole se desarrollo a mano con herramientas convencionales.

#### 4.5.1.5- Transferencia.

Los circuitos impresos diseñados, luego de ser armados y testeados, fueron usados como modelos para la fabricación de circuitos impresos en el Taller de Electrónica de la Carrera de Ingeniería Electrónica de la UNLaM. La Figura N°6 nos muestra las placas fabricados por los alumnos.

### 4.5.2- Makey Makey

El dispositivo conocido como Makey Makey consiste en un circuito con microcontrolador que se conecta a la PC por USB y permite emular pulsaciones de teclado y mouse utilizando una gran variedad de objetos como punto de contacto [16][17]. Este dispositivo, disponible comercialmente, puede aplicarse tanto para actividades lúdicas como para realizar interfaces adaptadas para interactuar con el computador. Debido a que el Makey Makey es un circuito de hardware y software libre y abierto, puede modificarse y adaptarse. Aprovechando esta característica, y debido la dificultad de obtenerlo en nuestro país, se planteo como objetivo realizar la adaptación del mismo para poder fabricarlo a bajo costo por cualquier estudiante o aficionado de electrónica.

El diseño de la placa fue desarrollado por miembros del proyecto como otra actividad niveladora. El armado y la puesta en marcha fue llevado a cabo por miembros del Lacie. Para las pruebas de campo de dichos dispositivos de cuenta con la asistencia de las Licenciadas S. L. Martínez, V. L. Cafasso, L. F. Motto.

### 4.5.2.1- Reglas de diseño

Se consideraron las mismas reglas de diseño que se emplearon para el modulo de Leds para robots Sumo, con la salvedad de la dimensión de la placa.

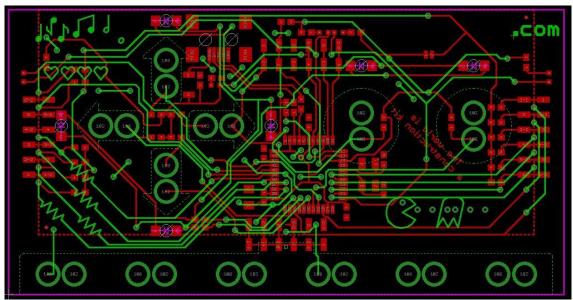

Es importante destacar que el diseño original del cual se parte es un diseño de dos capas, la Figura N°7 muestra el diseño original.

#### 4.5.2.2- Esquemático

En la Figura N°8 se presenta el esquemático Makey Makey.

Figura N°1. Esquemático del modulo de Leds.

Figura N°3. Circuito impreso modulo leds modelo 2.

La Figura N°4. Modulo de Leds armado.

Figura N°5. Modulo montado sobre un Robot Sumo.

Figura N°6. Placas fabricados por los alumnos.

## 4.5.2.3- Circuito impreso

En la Figura N°9 se presenta el circuito impreso diseñado.

# 4.5.2.4- Fabricación y armado

La fabricación y el armado de dichos módulos se llevo a cabo en las instalaciones y con materiales del Laboratorio abierto de la carrera de Ingeniería Electrónica (Lacie). La Figura N°10 y la Figura N°11 nos muestran el modulo armado.

Figura N°7. Diseño original de dos capas.

#### 4.5.2.5- Transferencia

Este proyecto fue presentado en el VIII Congreso Iberoamericano de Tecnologías de Apoyo a la Discapacidad, Iberdiscap 2015 [18][23].

## 4.5.3- Modulo de Acelerómetro para Robots Sumo.

Este diseño además de agregarle una funcionalidad extra a los Robot Sumo, la cual le permitirá detectar impactos, empujes y otros movimientos, familiarizaría a los participantes en el manejo de componentes de montaje superficial y pautas de diseño profesionales.

### 4.5.3.1- Reglas de diseño

A continuación se detallan las reglas y consideraciones que se debieron tomar en cuenta para el desarrollo del modulo, en este caso se tomaron como referencia las de la empresa CADIPEL [19], la cual fabrico los prototipos.

## 4.5.3.1.1-Características generales

- Materiales: FR4 y MCPCB (Metal Core PCB)

- Espesor: 1,6 mm.

- Dimensiones máximas: 280mm. x 340mm.

- Layers: 1 o 2 con PTH (Plated Through Hole)

- Espesor del cobre: 35um.

- Terminación: Cobre + OSP (Organic Solderability Preservative)

- Máscara antisoldante: Fotoimageable color verde

- Serigrafía de componentes: no

#### 4.5.3.1.2-Características del diseño

- Ancho de pista mínimo: 0,2mm. (8 mils)

- Separación mínima entre pistas: 0,2mm. (8 mils)

- Diámetro mínimo de agujero: 0,4mm. (16 mils)

- Diámetro mínimo de pad o vía: 0,8mm. (32 mils)

- Distancia de cobre a borde: 0,3mm. (12 mils)

#### 4.5.3.1.3-Información necesaria

- Archivos del diseño preferentemente en formato GERBER, también aceptamos archivos en Altium Designer, Eagle Professional, Proteus, Protel y Express Pcb (otros consultar).

- Cantidad de unidades a fabricar.

### 4.5.3.1.4- Consideración sobre el acelerómetro

El acelerómetro utilizado para este diseño fue el MMA8451Q [20], el cual posee un encapsulado QFN. Dicho encapsulado posee consideraciones de diseño [21] que fueron tenidas en cuenta al momento del diseño.

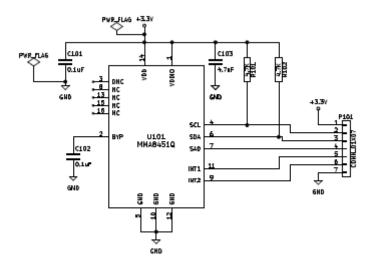

### 4.5.3.2- Esquemático

En la Figura N°12 se presenta el esquemático del modulo desarrollado.

### 4.5.3.3- Circuito impreso

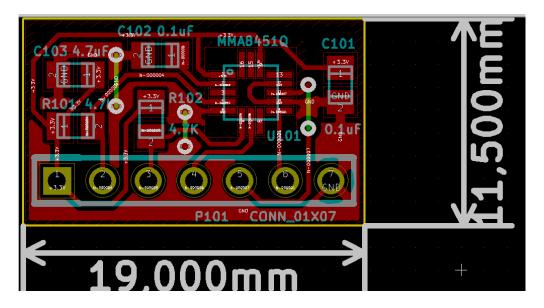

En la Figura N°13 se presenta el circuito impreso del módulo de acelerómetro.

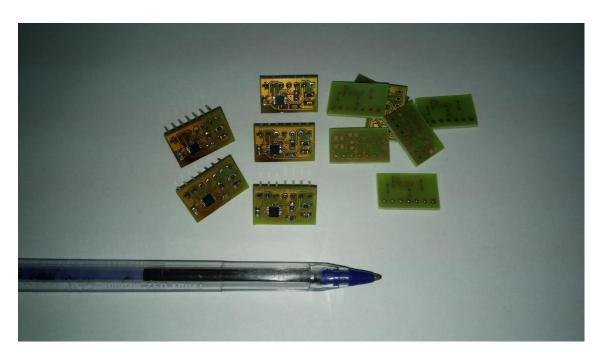

## 4.5.3.4- Fabricación y armado

La fabricación de estos circuitos impresos de los módulos acelerómetro se llevo a cabo por la firma CADIPEL. Esto fue posible gracias a un voucher que la firma había entregado al departamento de Electrónica como parte de pago de patrocinio realizado durante el VI Congreso de Microelectronica Aplicada desarrollado en la UNLaM. El armado de dichos módulos se llevo a cabo en las instalaciones y con materiales del Laboratorio abierto de la carrera de Ingeniería Electrónica (Lacie). La Figura N°14 nos las placas fabricadas.

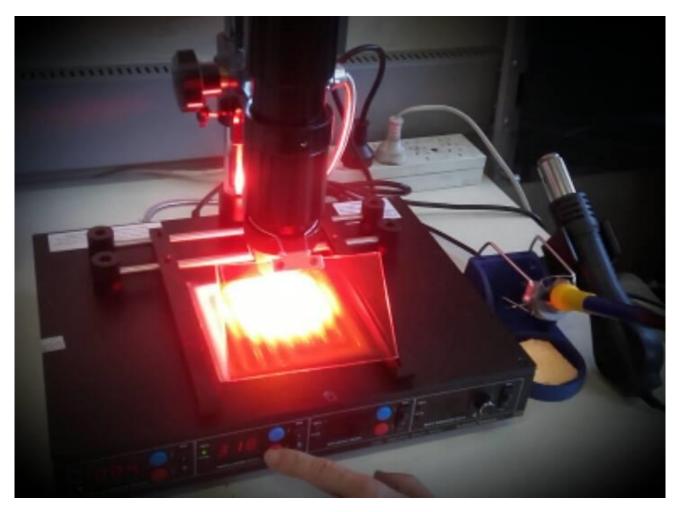

El armado por tratarse en su totalidad por componentes de montaje superficial, encapsulados 1206, 0805 y QFN, se realizo con una estación de soldado PACE MBT250 E [22].

Figura N°8. Esquemático Makey Makey.

Figura N°9. Circuito impreso diseñado.

Figura N°10. Makey Makey armado capa superior.

## 4.5.3.5- Fabricación y armado

Al momento no hay ninguna transferencia del diseño.

## 4.5.4- Diseño de EDU-CIAA-FSL

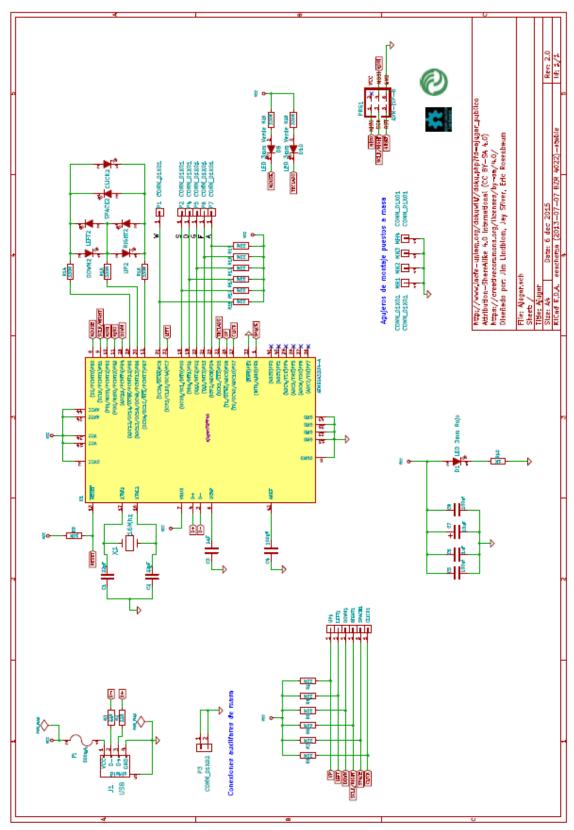

Tal como se hizo referencia en la sección 3.4 se participara en el desarrollo de la EDU-CIAA-FSL.

Como primera acción se contacto al coordinador de los diseños de EDU-CIAA, el Bioing. Eduardo Filomena. En el momento del contacto se encontraba el esquemático de la EDU-CIAA-FSL desarrollado y se estaba haciendo la ubicación de los componentes en el circuito impreso. Se acordó que nosotros continuaríamos con el desarrollo del circuito impreso y una vez finalizado se solicitaría la revisión del mismo antes de realizar la fabricación.

Figura N°11. Makey Makey armado capa inferior.

Figura N°12. Esquematico de modulo acelerómetro.

Figura N°13. Diseño de circuito impreso modulo acelerómetro

Figura N°14. Placas fabricadas del modulo acelerómetro.

## 4.5.4.1- Reglas de diseño

En la Tabla N°1 se detallan las reglas y consideraciones que se debieron tomar en cuenta para el desarrollo del modulo, en este caso se tomaron como referencia las de la empresa Mayer [23], una de las empresas de activa participación en el proyecto CIAA.

|                                     |              |              | ,            |              |

|-------------------------------------|--------------|--------------|--------------|--------------|

| TECNOLOGIA                          | 12 MILS      | 10 MILS      | 8 MILS       | 6 MILS       |

| DIAMETRO DE AGUJERO                 | 28 (0,70 mm) | 20 (0,50 mm) | 16 (0,40 mm) | 16 (0,40 mm) |

| DIAMETRO DE PAD O VIA               | 50 (1,27 mm) | 40 (1,00 mm) | 32 (0,80 mm) | 28 (0,70 mm) |

| ANCHO DE TRAZA                      | 12 (0,30 mm) | 10 (0,25 mm) | 8 (0,20 mm)  | 6 (0,15 mm)  |

| SEPARACION ENTRE<br>TRAZAS          | 12 (0,30 mm) | 10 (0,25 mm) | 7 (0,18 mm)  | 6 (0,15 mm)  |

| SEPARACION ENTRE TRAZA<br>Y PAD/VIA | 10 (0,25 mm) | 8 (0,20 mm)  | 6 (0,15 mm)  | 6 (0,15 mm)  |

| DISTANCIA DE COBRE A<br>BORDE       | 12 (0,30 mm) | 12 (0,30 mm) | 12 (0,30 mm) | 12 (0,30 mm) |

| ALTURA - TRAZO DE<br>LETRAS         | 48 - 8       | 36 -6        | 30 - 5       | 30 - 5       |

Tabla N°1. Especificaciones de diseño Mayer.

Como la el diseño incluye una interfaz USB 2.0, interfaz que puede llegar a manejar tazas de transmisión de datos de hasta 480Mbit/s, se hace necesario que las líneas de dicha interfaz cumplan con ciertas características para asegurar la integridad de la señal, así como para evitar la generación de interferencia electromagnética.

El tema de las líneas de la interfaz USB será tratado en un apartado independiente.

## 4.5.4.2- Esquemático

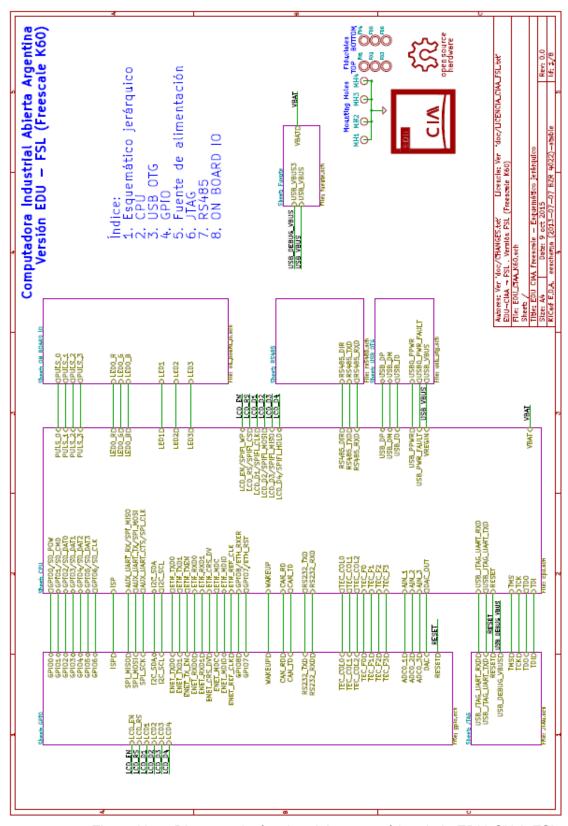

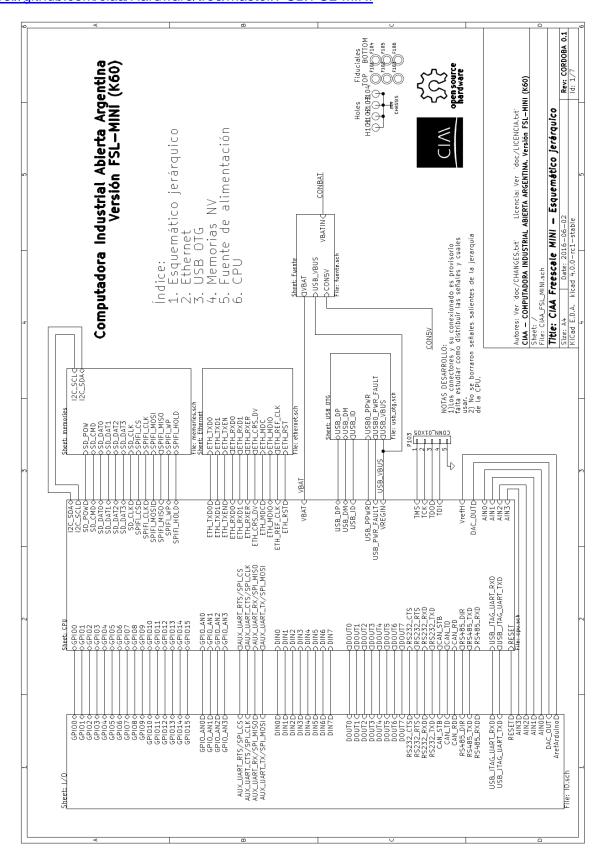

En la Figura N°15 se presenta el diagrama jerárquico del esquemático de la EDU-CIAA-FSL. Los esquemáticos de cada bloque no son incluidos en el informe pero se encuentran disponibles en el repositorio del proyecto [27].

Figura N°15.Diagrama jerárquico del esquemático de la EDU-CIAA-FSL.

# 4.5.4.3- Circuito impreso

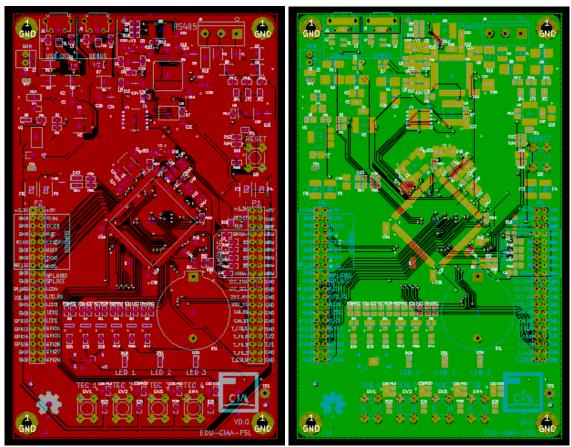

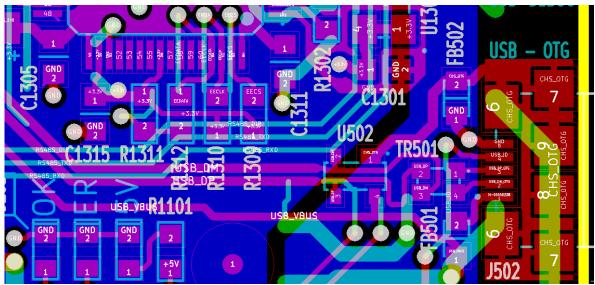

En la Figura N°16 se presenta el circuito impreso diseñado.

## 4.5.4.4- Fabricación y armado

#### 4.5.4.4.1- Periodo 2015

Actualmente el diseño se encuentra en etapa de revisión, una vez que este el OK por parte del coordinador, la misma se enviara a fabricar a la empresa Mayer. Es importante destacar que para poder realizar esto se deben contar con fondos, los cuales a la fecha no fueron asignados.

#### 4.5.4.4.2- Periodo 2016

La revisión de la placa fue realizada por el INTI, quienes presentaron para fines de febrero un informe sobre su evaluación y sugerencias de mejora, disponibles en el siguiente link:

https://github.com/ciaa/Hardware/blob/master/PCB/EDU-FSL/EDU\_CIAA\_K60/doc/revision1/EDU-CIAA-FSL\_Rev.pdf

Actualmente se están realizando las modificaciones a manos del responsable de las CIAA educativas. Para la fabricación del circuito impreso se dispone de un Voucher donado por Circuitos impresos Mayer, mientras que para los componentes se estaba en tratativas con Electrocomponentes S.A, el armado se efectuaría en las instalaciones de la UNLaM.

#### 4.5.4.5- Transferencia

#### 4.5.4.5.1- Periodo 2015

Al momento no hay ninguna transferencia del diseño. Pero una vez finalizada la revisión del diseño el mismo estará disponible para ser descargado de la página web del proyecto CIAA.

## 4.5.4.5.2- Periodo 2016

Si bien actualmente se están realizando modificaciones sobre el diseño, se encuentra disponible en el repositorio del proyecto CIAA, bajo licencia BSD, el diseño realizado junto con el informe de la gente del INTI.

https://github.com/ciaa/Hardware/tree/master/PCB/EDU-FSL

#### 4.5.4.6- Líneas de interfaz USB

Para el ruteo de las líneas de la interfaz USB de alta velocidad (2.0 o superior) en la página web del organización que se encarga de la estandarización de dicha interfaz [24], su puede encontrar una guía de diseño para plataformas USB de alta velocidad [25]. La misma posee una gran variedad de recomendaciones para llevar a cabo el ruteo. La principal de esta ellas es que las líneas sean llevadas hacia el conector a través de un par de líneas diferenciales de 90 ohm.

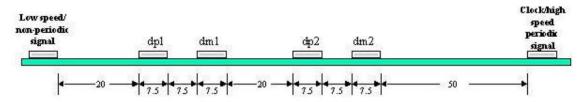

En el documento que se hace referencia en el párrafo anterior, se detallan también ancho de las pistas y el espaciado entre ellas, dichas recomendaciones se pueden ver en la Figura N°17, la unidad de medición en esta figura son las milésimas de pulgadas (mils).

Estas especificaciones están asociadas a un diseño de 4 capas, tal como se describe en el documento. Como el objetivo que buscan las plataformas EDU CIAA es ofrecer una alternativa de bajo costo, pensar en un diseño de 4 capas es ilógico, por lo tanto las recomendaciones detalladas deben ser adaptadas a un diseño de 2 capas.

Figura N°16. Circuito impreso diseñado

Figura N°17. Recomendaciones de ruteo.

Para esto se deben prestar mucha atención en el material utilizado como base de circuito impreso así como sus características, ya que cada material posee características eléctricas que afectaran la impedancia de las líneas. Una aproximación más cercana a lo que va ser nuestro diseño se puede encontrar en la Nota de aplicación de AN15.17 de Microchip [26], la cual realiza el diseño de una interfaz USB de alta velocidad en una placa de dos capas, cuyo material es FR-4 y cuyo espesor es de 1mm. La única diferencia que encontramos con las especificaciones de nuestro diseño es que el espesor de nuestra placa es de 1,6mm.

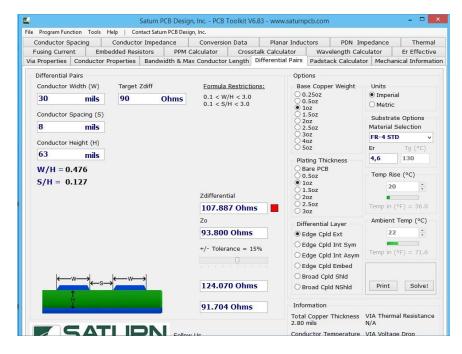

Por lo tanto, siguiendo las especificaciones para el ruteo del USB, la impedancia diferencial entre las señales USB\_DM y USB\_DP debe ser de 90 ohms ± 15% (76,5 ohms - 103,5 ohms) y utilizando la calculadora de Kicad (TrasLine -> Coupled Microstrip Line) y PCB Toolkit V6.83 para una placa FR4 de 1,6mm de espesor y el espesor de cobre de 35um (1 Oz.) se determinó un ancho de pista de 30 mils con una separación entre pistas de 8 mils lo que resulta en una impedancia diferencial de 107 ohms la cual está muy cerca del rango especificado, la Figura N°18 nos muestra la pantalla del software PCB Toolkit V6.83 utilizado para el cálculo de las líneas de la interfaz USB.

Figura N°18. Software PCB Toolkit V6.83.

Si se quisiese acercar más a la especificación se deberá aumentar el ancho de pista o disminuir la separación entre las pistas. La primera alternativa resulta poco práctica y la segunda redunda en un aumento en el costo de fabricación.

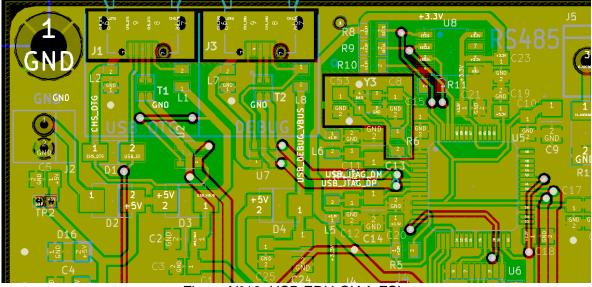

En la figura N°19 muestra un zoom del área del conector USB, donde se puede ver el ancho de las pistas en comparación con el conector. La figura N°20 muestra las mismas líneas pero en el diseño de la CIAA- FSL, el cual fue desarrollado en 4 capas. Se puede apreciar que la pistas de este último diseño son mas angostas, los cálculos dieron 18mils con una separación de 8 mils.

Figura N°19. USB EDU-CIAA-FSL.

Figura N°20. USB CIAA-FSL.

#### 4.5.5- Ponchos

En el contexto del proyecto CIAA se define como poncho a los módulos conectables para montarse sobre el módulo procesador EDU-CIAA. Estos módulos extienden la funcionalidad de la EDU-CIAA agregando el hardware necesario para distintas aplicaciones [28]. Lo que en nuestro resumen del proyecto llamamos placas auxiliares.

### 4.5.5.1- Selección del Poncho a realizar.

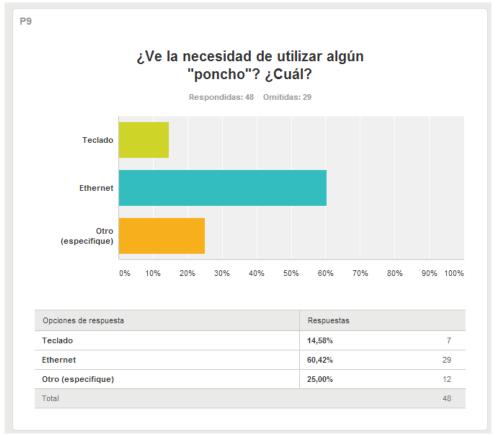

Desde la ACSE, una vez finalizada la primera proventa de placas EDU-CIAA-NXP se realizo una encuentra sobre el futuro uso de dicha plataforma. Los resultados de la misma están disponibles en la web [29]. Uno de los puntos consultados fue "¿Ve la necesidad de utilizar algún "poncho"? ¿Cuál?". En la Figura N°21 se muestras los resultados de dicha encuesta.

En función de ello se decidió el desarrollo de este "poncho".

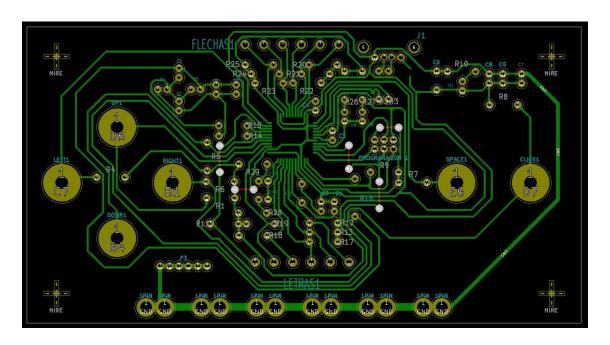

## 4.5.5.2- Reglas de diseño

Como regla de diseño para esta placa se utilizaron las mismas que se emplearon para el diseño de la EDU-CIAA-FSL, las cuales son las especificaciones de Circuitos Impresos Mayer, ver sección 4.5.4.1.

Consideraciones especiales asociadas a la interfaz Ethernet fueron tenidas en cuenta, las mismas serán tratadas en un apartado independiente.

#### 4.5.5.3- Esquemático

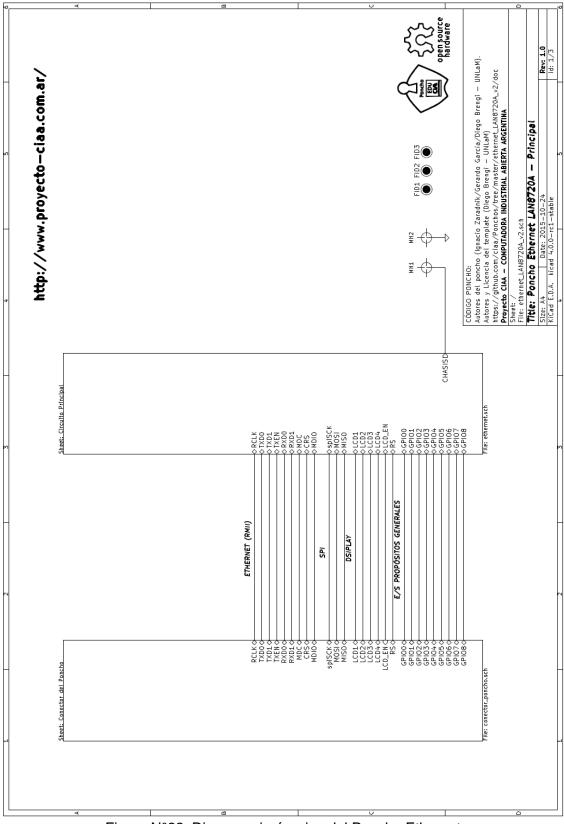

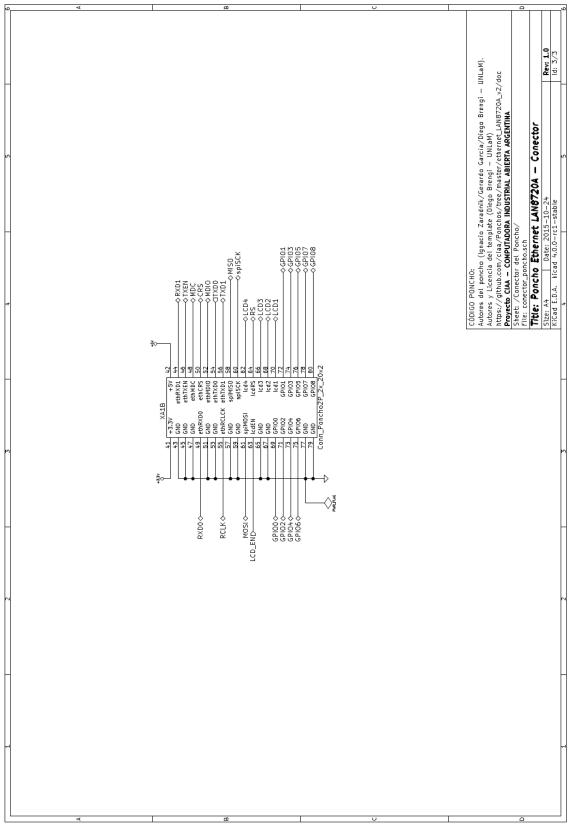

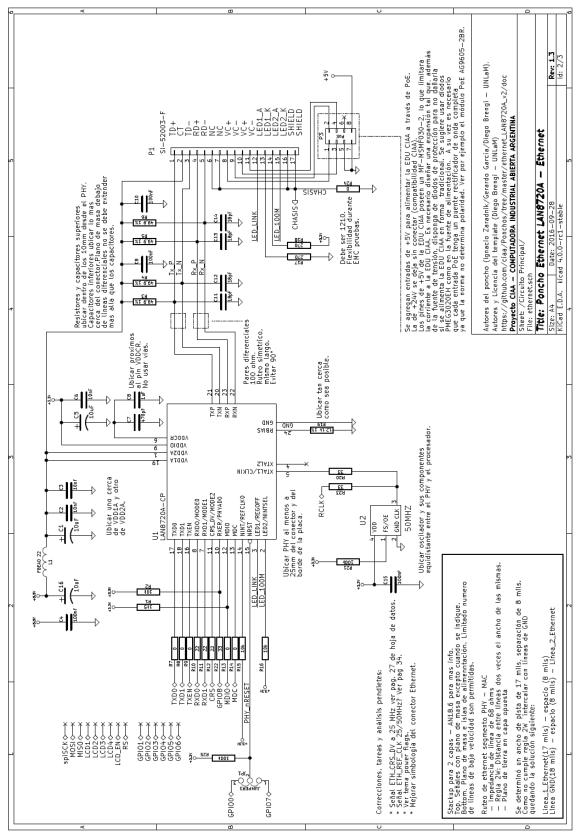

En la Figura N°22, N°23 y N°24 se presenta el diagrama jerárquico del esquemático del Poncho Ethernet y los diagramas circuitales.

Los esquemáticos presentados en este informen difieren levemente de lo presentados en el informe de avance, esto es a raíz de que se estuvieron realizando cambios.

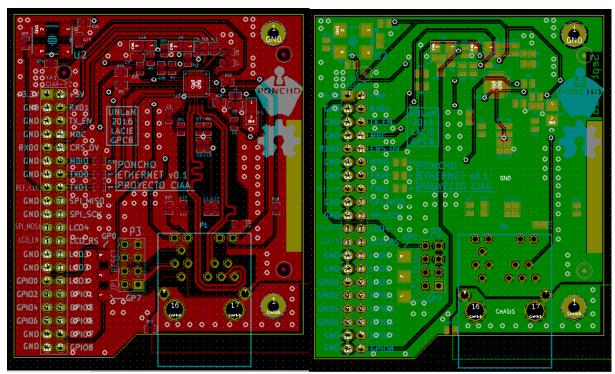

### 4.5.5.4- Circuito impreso

En la Figura N°25 se presenta el circuito impreso diseñado.

Figura N°21. Resultados de la encuesta.

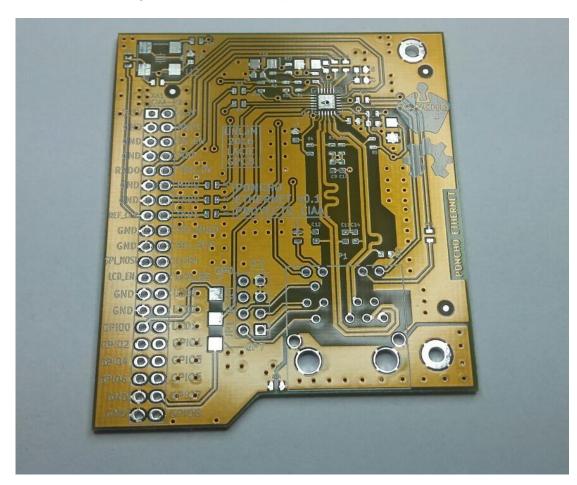

### 4.5.5.5- Fabricación y armado

En la Figura N°26 se presenta el circuito impreso del poncho Ethernet. Al momento de presentar este informe no se realizo el armado ya que los componentes, los cuales son aportados por Electrocomponentes S.A., están siendo importados. La tabla N°1, detalla los componentes que forman parte de la misma.

#### 4.5.5.6- Líneas de interfaz Ethernet

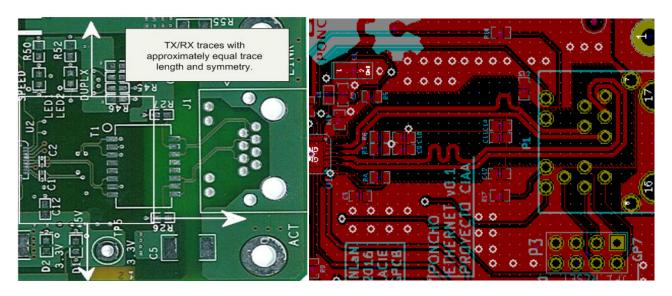

Para el diseño del par diferencial de la interfaz Ethernet se tomaron como referencia la documentación asociada al chip empleado, LAN8720 de NXP [30][31][32][33][34].

La especificación 802.3-2005 requiere que las líneas TX y RX corran en modo diferencial. Las líneas TXP y TXN son un par diferencial y es necesario que sea diseñado con una impedancia diferencial de 100 ohm. De forma similar debe sucede para las líneas RXP y RXN.

La impedancia diferencial de los pares debe ser mantenida durante todo el layout del mismo. Para diferentes dieléctricos, espesores del cobre o stack up de la placa, el ancho de las líneas y la separación entre ellas debe ser recalculada.

El par diferencial debe mantener simetría. Las líneas TXP y TXN deben tener el mismo largo y deben ser simétricas con respecto a la forma, el largo y la cantidad de vías. De forma similar debe suceder con RXP y RXN.

La figura N°27 presenta un ejemplo de cómo deben ser las líneas y nuestro diseño. Para realizar los cálculos del ancho de las pistas se utilizo la herramienta disponible en Kicad, la cual para una

placa de FR4 y de espesor de 1,6mm arrojo un ancho de pista de 0,55mm (aprox 22mil) y una separación entre ellas de 0,25mm (aprox. 10mil).

Figura N°22. Diagrama jerárquico del Poncho Ethernet.

Figura N°23. Conectores del Poncho Ethernet.

Figura N°24. Esquemático del Poncho Ethernet.

Figura N°25. Circuito impreso del Poncho Ethernet.

Figura N°26. Circuito impreso del Poncho Ethernet fabricado.

La Tabla N°1. Lista de componentes del Poncho Ethernet.

| Refs              | Value       | Desc                                                    | Manf#              |                       | Qty |

|-------------------|-------------|---------------------------------------------------------|--------------------|-----------------------|-----|

| U2                | SOMHZ       | 50MHz HCMOS XO Standard Oscillator SMD 3.3V 30mA En/Dis | ASV-50.000MHZ-E-T  | 535-10087-1-ND        | 5   |

| P1                | SI-52003-F  | RJ45 Magjack Connector TH 10/100 Base-T, AutoMDIX, PoE  | SI-52003-F         | 380-1119-ND           | 5   |

| L1                | FBEAD 22    | FERRITE BEAD 22 OHM 0603 1LN                            | BK1608HS220-T      | 587-1869-1-ND         | 5   |

| C4,C9,C10,C15     | 100nF       | CAP CER 0,1UF 16V 10% X7R 0603                          | C0603C104K4RACTU   | 399-1096-1-ND         | 20  |

| U1                | LAN8720A-CP | 4/4 Transceiver Full RMII 24-QFN (4x4)                  | LAN8720A-CP-TR     | LAN8720A-CP-CT-ND     | 5   |

| XA1               | Conn_20x2   | 40P Header BTB Conn Gold 50mils 1.27mmTHole             | M50-3502042        | 952-1387-ND           | 5   |

| R10-R12           | 22          | RES 22 OHM 1/10W 5%                                     | RC0603JR-0722RL    | 311-22GRCT-ND         | 15  |

| C11-C14           | 18pF        | CAP CER 18PF 50V 5% NP0 0603                            | C0603C180J5GACTU   | 399-1052-1-ND         | 20  |

| R3-R6             | 49,91%      | RES 49,9 OHM 1/10W 1% 0603 SMD                          | RC0603FR-0749R9L   | 311-49.9HRCT-ND       | 20  |

| R7-R9,R13,R14,R24 | 0           | RES SMD 0.00HM JUMPER 1/10W 0603                        | CR0603-J/-000ELF   | CR0603-J/-000ELFCT-ND | 30  |

| R17,R18           | 270         | RES 270 OHM 1/10W 5% 0603 SMD                           | RC0603JR-07270RL   | 311-270GRCT-ND        | 10  |

| C2,C3,C6          | 10nF        | CAP CER 10000PF 50V 10% X7R 0603                        | C0603C103K5RACTU   | 399-1091-1-ND         | 15  |

| R2,R15,R16        | 10k         | RES 10K OHM 1/10W 5% 0603 SMD                           | RC0603JR-0710KL    | 311-10KGRCT-ND        | 15  |

| R20,R22,R23       | 33          | RES 33 OHM 1/10W 5% 0603 SMD                            | CR0603-JW-330GLF   | CR0603-JW-330GLFCT-N  | 15  |

| 83                | 1uF         | CAP CER 1UF 16V 10% X7R 0603                            | C0603C105K4RACTU   | 399-7847-1-ND         | 5   |

| Р3                | PoE         | 8 Pin Header Conn Gold 50 mils 1.27mm THole             |                    |                       | 5   |

| C1,C5,C16         | 10uF        | CAP TANT 10UF 6.3V 10% 1206                             | T491A106K006AT7280 | 399-3683-1-ND         | 15  |

| R21,R25           | 100k        | RES SMD 100K OHM 5% 1/10W 0603                          | CR0603-JW-104ELF   | CR0603-JW-104ELFCT-N  | 10  |

| C7                | 470pF       | CAP CER 470PF 50V 10% X7R 0603                          | C0603C471K5RACTU   | 399-1075-1-ND         | 5   |

| R1                | 1k5         | RES 1.5K OHM 1/10W 5% 0603 SMD                          | RC0603JR-071K5L    | 311-1.5KGRCT-ND       | 5   |

| R19               | 12.1k 1%    | RES SMD 12.1K OHM 1% 1/10W 0603                         | RC0603FR-0712K1L   | 311-12.1KHRCT-ND      | 5   |

Figura N°27. Diseño de pares diferenciales.

Ante la imposibilidad de mantener la simetría y el largo, se opto por mantener el mismo largo en ambas líneas del par diferencial, ya que esta posee una mayor relevancia.

#### 4.5.5.7- Transferencia

#### 4.5.5.7.1- Periodo 2015

Al momento no hay ninguna transferencia del diseño. Pero una vez finalizada la revisión del diseño el mismo estará disponible para ser descargado de la página web del proyecto CIAA.

### 4.5.5.7.2- Periodo 2016

Si bien actualmente no se ha finalizado el armado y las pruebas, el diseño se encuentra disponible en el repositorio del proyecto CIAA, bajo licencia BSD.

https://github.com/ciaa/Ponchos/tree/master/ethernet LAN8720A v2

#### 4.5.6- Poncho Modelos

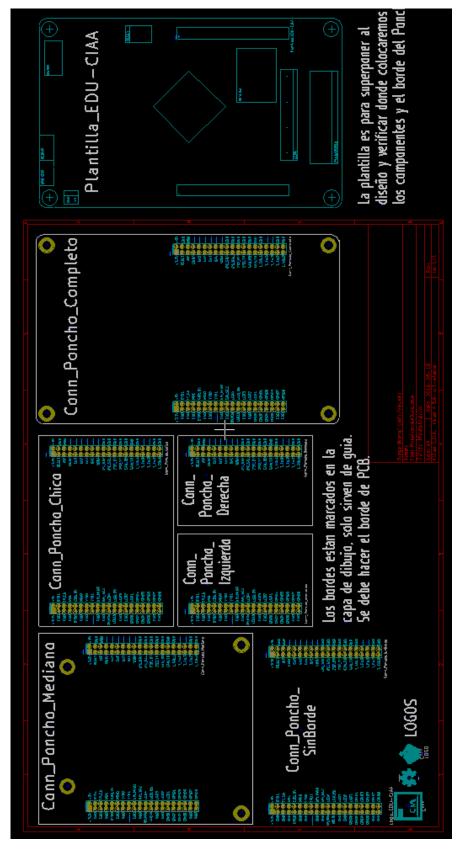

A fin de facilitar futuros diseños de ponchos (placas auxiliares para las placas EDU-CIAA) se diseñaron un conjunto de ponchos modelos. Los mismos son simplemente una placa con tira de pines, sobre la cual se realizará el diseño que se desee. Esto busca estandarizar el formato de los ponchos.

### 4.5.6.1- Reglas de diseño

Como regla de diseño para esta placa se utilizaran las mismas que se emplearon para el diseño de la EDU-CIAA-FSL. Las cuáles son las especificaciones de Circuitos Impresos Mayer, ver sección 4.5.4.1.

### 4.5.6.2- Esquemático y Circuito impreso

Se han desarrollado distintos versiones de ponchos modelo, entre ellas encontramos: poncho grande/completo, poncho mediano, poncho chico, poncho derecho, poncho izquierdo y poncho

básico. Por no representar ningún aporte significativo, se omite una imagen del esquemático. La figura N°28 nos muestra una imagen comparativa de todos los modelos.

Figura N°28. Ponchos modelos.

## 4.5.6.3- Fabricación y Armado

Por no tener ninguna funcionalidad en si mismo, no se ha fabricado ninguno de los ponchos modelo.

#### 4.5.6.4- Transferencia

Los distintos ponchos modelos son utilizados en la cátedra de "Diseño de Circuitos Impresos" de la especialización/maestría de sistemas embebidos de la UBA.

http://laboratorios.fi.uba.ar/lse/especializacion.html

Los ponchos modelos están disponibles en:

https://github.com/ciaa/Ponchos/tree/master/modelos

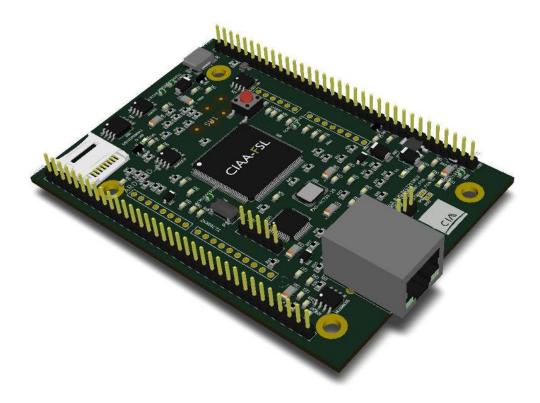

#### 4.5.7- CIAA-NUCLEO-FSL / FSL-MINI

La CIAA-NUCLEO-FSL es un versión reducida de la CIAA-FSL, la misma fue pensada como reemplazo de los módulos Rabbit [35], para aquellas aplicaciones de bajo costo que requieran conexión vía Ethernet. Este proyecto surgió como una inquietud del Ing. Esteban Volentini, de la firma Equiser[36].

Se contemplo que posea conectores de expansión tipo pinera simple para poder agregarle fácilmente electrónica adicional específica de cada aplicación. El objetivo es resolver la parte compleja como el procesador y el Ethernet en un PCB de 4 capas, y luego dejar al usuario el desarrollo de la electrónica restante.

## 4.5.7.1- Esquemático

En la Figura N°29 se presenta el diagrama jerárquico del esquemático de la CIAA-NUCLEO-FSL. Los esquemáticos de cada bloque no son incluidos en el informe pero se encuentran disponibles en el repositorio del proyecto, detallado en la sección 4.5.7.4.

### 4.5.7.2- Circuito impreso

Al momento del informe solo se ha realizado la ubicación de los componentes. En la figura N°30 se presenta una imagen 3D de la placa y sus componentes.

### 4.5.7.3- Fabricación y Armado

Por encontrase aun en proceso de diseño no se han fabricado aun placas prototipos.

#### 4.5.7.4- Transferencia

Este diseño surgió desde un primer momento como una transferencia a una empresa. Si bien el diseño está encuadrado bajo el proyecto CIAA, una vez finalizado tendrá una aplicación inmediata en una empresa del rubro electrónico [36].

Que el diseño se encuadre bajo el proyecto CIAA, permite que el diseño desarrollado no sea tan solo utilizado por una empresa, sino por toda aquella que lo considere adecuado para sus proyectos. El trabajo realizado hasta el momento se encuentra disponible en:

Figura N°29. Esquemático Jerárquico de CIAA-NUCLEO-FSL.

Figura N°30. Imagen 3D de la placa CIAA-NUCLEO-FSL.

## 4.6. Instrumentos de Recolección y Medición de Datos

Las actividades detalladas en las secciones 4.5.1, 4.5.2, 4.5.3 y 4.5.6 fueron consensuadas internamente entre los miembros del grupo, por lo que no se realizo ningún tipo de encuesta. Para el diseño de dichos circuitos impresos se utilizo la información provista por los fabricantes de los componentes electrónicos, disponible en las páginas web de los mismos.

La actividad detallada en la sección 4.5.4, EDU-CIAA-FSL, fue consensuada con el coordinador de las placas educativas dentro del proyecto CIAA, el Biong Eduardo Filomena. Para el diseño de dicho circuito impreso se utilizo las especificaciones disponibles en la web del proyecto CIAA, ver ANEXO III, así como también la información provista por los fabricantes de los componentes electrónicos, disponible en las páginas web de los mismos.

La actividad detallada en la sección 4.5.5, fue seleccionada a raíz de una encuesta llevada adelante por la Asociación Civil para la Investigación, Promoción y Desarrollo de los Sistemas Embebidos (ACSE), mas detalles de esta se encuentra en la sección 4.5.5.1. Para el diseño de dicho circuito impreso se está utilizando la información provista por los fabricantes de los componentes electrónicos, disponible en las páginas web de los mismos.

La actividad detallada en la sección 4.5.7, por tratarse inicialmente de un desarrollo para una empresa, fue consensuada con el Ing. Esteban Volentini representante de la empresa Equiser [36]. Para el diseño de dicho circuito impreso se está utilizando la información provista por los fabricantes de los componentes electrónicos, disponible en las páginas web de los mismos, así como consideraciones de compatibilidad mecánica con los módulos Rabbit, solicitud de la empresa.

## 4.7. Confiabilidad y Validez de la Medición

Los diseños detallados en las secciones 4.5.1, 4.5.2, 4.5.3 y 4.5.6, por tratarse de trabajos de nivelación y de complejidad reducida, fueron controlados y validados por los miembros de mayor experiencia del grupo de investigación. El objetivo de dichos diseños fue la familiarización de los alumnos participantes con la herramienta y los conceptos básicos.

El diseño detallado en la sección 4.5.4, tuvo un primer control llevado a cabo por el coordinador de las placas educativas dentro del proyecto CIAA, el Biong Eduardo Filomena, con apoyo del Biong Gonzalo Cuenca, ambos de la Universidad Nacional de Entre Ríos.

A continuación se detallan los comentarios realizados:

- USB. Si bien no es crítico el ruteo de una interfaz USB Full Speed por su baja velocidad (12Mbps), según la especificación USB las líneas diferenciales deben tener una impedancia característica diferencial de 90 ohm +/- 15 %. Para este fin, se listan a continuación una serie de recomendaciones:

- Ubicar todos los componentes involucrados con las señales USB en la cara superior del PCB.

- Realizar el trazado de las pistas diferenciales en la cara superior del PCB sin realizar cambios de planos.

- Para cruzar DM y DP (debido al orden de los pines en el conector), utilizar una pista por debajo del choque de modo común. Intentar que las pistas diferenciales se mantengan a la misma distancia y que tengan el mismo largo total (utilizar la información que provee Kicad al seleccionar las pistas).

- Con respecto al ancho de las pistas, intentar aumentarlo a 20 mils y mantener una separación de 8 mils como máximo.

#### SILKSCREEN

- Unificar los tamaños de indicadores serigráficos de componentes. Una de las teorías es que TODO tenga el mismo tamaño. Otra es que todos los componentes tengan el mismo tamaño y reservar una tipografía legible a simple vista para conectores e indicadores clave para el proyecto (ej. conectores VCC, GND, testpoints, etc.)

- o Evitar que los indicadores queden arriba de pads y vías.

Realizados estos cambios, personal del departamento de micro y nanotecnología del INTI realizaron una revisión y efectuaron una serie de recomendaciones antes mencionadas.

# https://github.com/ciaa/Hardware/tree/master/PCB/EDU-FSL/EDU\_CIAA\_K60/doc/revision1

El diseño detallado en la sección 4.5.5, tuvo una revisión por el coordinador de hardware del proyecto CIAA, el Ing. Pablo Ridolfi, actual coordinador del proyecto. Las sugerencias fueron menores, por lo que se envió a fabricar tan pronto como fue posible.

El diseño detallado en la sección 4.5.7, aun continua en desarrollo.

### 4.8. Métodos de Análisis Estadísticos

Los mismos no son aplicados en este proyecto.

### 4.9. Resultados

Entre los resultados del proyecto podemos citar:

- La generación de recursos humanos en el diseño de circuitos impresos.

- La participación por parte de la Universidad en un proyecto abierto que integra distintos miembros del ámbito académico e industrial.

- La presentación de un paper asociado al trabajo realizado durante el proyecto.

- El dictado de un curso sobre consideraciones de diseño de circuitos impresos en el marco de un curso de capacitación del INTI sobre Kicad.

- El diseño de una plataforma educativa para la enseñanza de Sistemas Embebidos

- El diseño de placas auxiliares para la plataforma educativa para la enseñanza de Sistemas Embebidos

- Lograr la interacción directa con la industria a través del desarrollo de la CIAA-NUCLEO-FSL.

- Equipar el lab. de Electrónica con una estación de soldado por Infrarrojo, figura N°31, la cual

junto con el resto del equipamiento disponible brinda a los alumnos las facilidades para

encarar desarrollos de mayor complejidad.

Figura N°31. Estación de soldadura por Infrarrojo.

### 4.10. Discusión

La misma no es aplicada en este proyecto.

### 5. Conclusiones

### 5.1- Periodo 2015

Se ha cumplido parcialmente con las actividades planteadas inicialmente, esto se debe principalmente a no haber contado con el presupuesto asignado, y en menor medida a las tareas niveladoras implementadas.

El equipo de trabajo se desempeño en forma adecuada, respetando los plazos de tiempos definidos en el momento de la organización de las tareas.

En referente objetivo secundario, el estudio de las distintas consideraciones de diseño para placas de circuitos impresos que permita la integración de dispositivos con mayores prestaciones a los desarrollos nacionales, se logro satisfactoriamente, ya que se realizado el estudio del diseño de líneas de impedancia controlada y pares diferenciales. Ambas importantes para diseños de interfaces USB y Ethernet.

### 5.2- Periodo 2016

Los objetivos del proyecto se lograron cumplir casi en su totalidad:

Se elaboró una placa de desarrollo para la enseñanza de sistemas embebidos, la cual se encuadrará en el marco del proyecto CIAA. Si bien aún no se finalizo su fabricación y armado, el objetivo primordial fue logrado.

Se formaron recursos humanos para el diseño y manufactura de placas de circuitos impresos, tanto alumnos como docentes de la universidad. Se generó simultáneamente un lugar donde los alumnos de la carrera de Ingeniería Electrónica puedan adquirir conocimientos extracurriculares de gran importancia para su inserción en el mercado actual.

Se logró una interacción con distintas empresas, universidades e instituciones que enriqueció al grupo de trabajo. Si bien dicha interacción generó demoras, también aportó puntos de vista que no se tenían en cuenta.

Si bien el proyecto ha finalizado desde el punto de vista formal, la actividad continuará en el marco del Laboratorio Abierto de la Carrera de Ingeniería Electrónica. Se prevé para el año 2017 el armado y la puesta en marcha de los diseños abordados, así como el dictado de uno o más cursos sobre la temática estudiada (diseño de circuitos impresos).

### 6. Bibliografía

- [1] http://www.ilo.org/sector/activities/sectoral-meetings/lang--es/index.htm, última visita 03/12/2015.

- [2] <a href="http://www.ilo.org/sector/activities/sectoral-meetings/WCMS">http://www.ilo.org/sector/activities/sectoral-meetings/WCMS</a> 176829/lang--es/index.htm, última visita 03/12/2015.

- [3] http://www.ipc.org/ContentPage.aspx?pageid=IPC-Fact-Sheet-Spanish, última visita 03/12/2015.

- [4] http://www.proyecto-ciaa.com.ar/devwiki/doku.php?id=start, última visita 04/12/2015.

- [5] https://en.wikipedia.org/wiki/Comparison\_of\_EDA\_software, última visita 04/12/2015

- [6] http://www.ohwr.org/projects/cern-kicad/wiki, última visita 04/12/2015

- [7] http://www.ohwr.org/projects/cern-kicad/wiki/Donor-recognition, última visita 04/12/2015.

- [8] http://fpgalibre.sourceforge.net/hard.html#tp18, última visita 04/12/2015.

- [9] http://blog.elphel.com/2015/04/trying-out-kicad/, última visita 04/12/2015.

- [10] https://olimex.wordpress.com/tag/kicad/, última visita 04/12/2015.

- [11] http://www.sase.com.ar/asociacion-civil-sistemas-embebidos/files/2013/11/Propuesta-

- Computadora-Industrial-Abierta-Argentina-ACSE-CADIEEL-v2.5.pdf, última visita 04/12/2015.

- [12] http://www.proyecto-

- <u>ciaa.com.ar/devwiki/doku.php?id=desarrollo:hardware:ciaa\_nxp:ciaa\_nxp\_inicio</u>, última visita 04/12/2015.

- [13] http://www.provecto-

- <u>ciaa.com.ar/devwiki/doku.php?id=desarrollo:hardware:ciaa freescale:ciaa freescale inicio,</u> última visita 04/12/2015.

- [14] <a href="http://www.proyecto-ciaa.com.ar/devwiki/doku.php?id=desarrollo:edu-ciaa:edu-ciaa-nxp">http://www.proyecto-ciaa.com.ar/devwiki/doku.php?id=desarrollo:edu-ciaa:edu-ciaa-nxp</a>, última visita 04/12/2015.

- [15] <a href="http://www.proyecto-ciaa.com.ar/devwiki/doku.php?id=aportes">http://www.proyecto-ciaa.com.ar/devwiki/doku.php?id=aportes</a> desarrolladores, última visita 04/12/2015.

- [16] Silver, J., & Shaw, D. (2012). Makey Makey: improvising tangible and nature-based user interfaces. Proceedings of the Sixth International Conference on Tangible Embedded, Embodied Interaction, 367–370. Disponible en: <a href="http://web.media.mit.edu/~ericr/papers/silver-makeymakey-TEI.pdf">http://web.media.mit.edu/~ericr/papers/silver-makeymakey-TEI.pdf</a>, última visita 04/12/2015.

- [17] MIT Media Lab. "MaKey MaKey, An Invention Kit for Everyone".

- http://web.media.mit.edu/~ericr/makeymakey/, última visita 04/12/2015.

- [18] http://iberdiscap2015.com/, última visita 04/12/2015.

- [19] http://cadipel.com.ar/project/fabricacion-rapida-de-pcbs/, última visita 04/12/2015.

- [20] Freescale, "MMA8451Q, 3-Axis, 14-bit/8-bit Digital Accelerometer", Rev. 9.1, 06/2015.

- [21] Freescale, MMA845xQ Design Checklist and Board Mounting Guidelines, Rev. 2, 10/2012

- [22] https://www.paceworldwide.com/products/conductive-rework-systems/mbt-250/mbt-250esdtp, última visita 04/12/2015.

- [23] http://www.mayerpcb.com/index.php?id=info-tecnica, última visita 04/12/2015.

- [24] http://www.usb.org/home

- [25] INTEL, "High Speed USB Platform Design Guidelines", Rev 1.0.

- [26] Microchip, "AN15.17. PCB Layout Guide for USB Hubs"

- [27] https://github.com/ciaa/Hardware/tree/master/PCB/EDU-FSL, última visita 04/12/2015.

- [28] <a href="http://www.proyecto-ciaa.com.ar/devwiki/doku.php?id=desarrollo:edu-ciaa:ponchos">http://www.proyecto-ciaa.com.ar/devwiki/doku.php?id=desarrollo:edu-ciaa:ponchos</a>, última visita 04/12/2015.

- [29] https://es.surveymonkey.com/results/SM-DVCQ99TY/, última visita 04/12/2

- [30] Microchip, "AN18.6 SMSC Ethernet Physical Layer Layout Guidelenes", Revision 0.8.

- [31] Microchip, "EVB8720 Evaluation Board Schematic" Revision 1.3.

- [32] Microchip, "EVB8720 Evaluation Board User Manual" Revision 1.2.

- [33] Microchip, "LAN8720A/LAN8720Ai, Small Footprint RMII 10/100 Ethernet Transceiver with HP Auto-MDIX Support", Revision 1.4.

- [34] Microchip, "Schematic Checklist for LAN8720", Revision D.

- [35] https://www.digi.com/products/embedded-systems/system-on-modules, última visita 29/12/2016

- [36] <a href="http://www.equiser.com.ar/">http://www.equiser.com.ar/</a>, última visita 29/12/2016.

### Anexo I

### Rendición de gastos del proyecto de investigación

## Anexo II La industria Electrónica

### A2- La Industria Electrónica

En la sede de la Organización Internacional del Trabajo (OIT) en Ginebra se reúnen varias veces al año representantes de los gobiernos y de las organizaciones de empleadores y de trabajadores de distintos países y regiones para participar en reuniones sectoriales tripartitas internacionales y en foros de diálogo mundial. Basándose en las investigaciones más recientes de la OIT, los representantes tripartitos se reúnen para debatir sobre las cuestiones emergentes, así como sobre las principales tendencias y desafíos de su sector.

El consenso que se alcanza durante estas reuniones sectoriales da lugar a recomendaciones destinadas a la adopción de políticas y medidas en los distintos sectores. Estas recomendaciones, que se adoptan al final de las reuniones, sirven de base para la elaboración de políticas y de programas nacionales y proporcionan orientación a los mandantes tanto en el plano internacional como nacional [1].

Por lo tanto, toda actividad con cierta relevancia a nivel mundial es debatida en este tipo de reuniones sectoriales. Es tal la importancia de la industria electrónica que durante el año 2007 se llevo a cabo la "Reunión tripartita sobre la fabricación de componentes electrónicos para las industrias de las tecnologías de la información: el cambio de las necesidades con respecto a la mano de obra en una economía mundializada". Si bien los temas debatidos y sus conclusiones no son de la incumbencia de este proyecto, dicha reunión muestra la importancia del rubro [2].

Otro indicador que nos muestra la importancia que tiene la industria Electrónica es que desde 1957 existe una existe una asociación que da servicio a la industria electrónica, específicamente a diseñadores de circuitos impresos, fabricantes de circuitos impresos y a empresas de fabricación de electrónica. Además, los especificadores y compradores de circuitos impresos y servicios de ensamblaje (fabricantes de equipos originales), empresas de capacitación, proveedores, instituciones educativas, agencias gubernamentales, laboratorios y proveedores de servicios se benefician de los estándares de IPC así como de su participación en la organización. Esta asociación lleva el nombre de IPC Association Connecting Electronics Industries, y está acreditado por la ANSI (Industria de Estándares Nacional Americana, por sus siglas en inglés) como una organización de desarrollo de estándares [3].

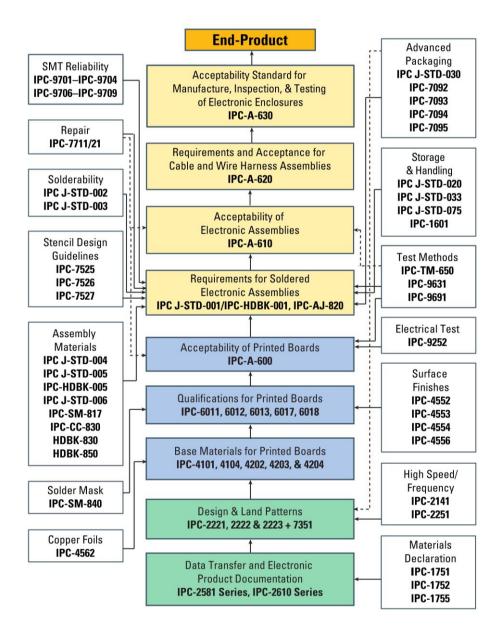

La figura N°A2-1 nos muestra una estructura en árbol de los estándares desarrollados por la IPC para el desarrollo de un dispositivo Electrónico, desde su concepción hasta obtener el producto final. En esta figura podemos ver claramente que los estándares están separados en tres grupos, el primero de ellos dedicado a la documentación y al diseño de circuitos impresos, el segundo de ellos dedicado a la fabricación de los circuitos impresos y finalmente el tercero de ellos dedicado a la el ensamblaje de lo ellos. Como el objetivo del proyecto es el desarrollo de plataformas educativas para la enseñanza de Sistemas Embebidos, serán de vital importancia estos estándares.

Independiente de las distintas organizaciones y asociaciones a través de las cuales se puede percibir la importancia de la industria electrónica, en la Argentina la Asociación Civil para la Investigación, Promoción y Desarrollo de los Sistemas Embebidos (ACSE) junto con la Cámara Argentina de Industrias Electrónicas, Electromecánicas y Luminotécnicas (CADIEEL) vienen impulsando desde fines del 2013 el proyecto CIAA (Computadora Industrial Argentina Abierta) [4] con los objetivos:

- Impulsar el desarrollo tecnológico nacional, a partir de sumar valor agregado al trabajo y a los productos y servicios, mediante el uso de sistemas electrónicos, en el marco de la vinculación de las instituciones educativas y el sistema científico-tecnológico con la industria.

- Darle visibilidad positiva a la electrónica argentina.

Generar cambios estructurales en la forma en la que se desarrollan y utilizan en nuestro país los conocimientos en el ámbito de la electrónica y de las instituciones y empresas que hacen uso de ella.

Figura N°A2-1. Estándares IPC.

En este marco se viene desarrollando distintas plataformas de hardware, firmware y software para sistemas embebidos, con la participación sin fines de lucro de empresas privada e instituciones.

# Anexo III Proyecto CIAA

### A3- Proyecto CIAA.

### A3.1- Propuesta Innovadora

La CIAA es la primera iniciativa a nivel internacional que conjuga simultáneamente tres elementos cuya concurrencia la transforman en una propuesta única e innovadora:

- 1. Es industrial porque dispone de diferentes mecanismos de protección eléctrica contra fallas o sobrecargas. De esta forma brinda una base para diseñar sistemas capaces de considerar cuestiones de disponibilidad, confiabilidad, verificación, validación y seguridad intrínseca, además de la posibilidad de certificar normas internacionales como las IEC 61131 y la IEC 61508, contemplando criterios de robustez ante interferencia electromagnética, sobrecarga de las salidas, vibraciones mecánicas, estrés térmico, perturbaciones en la tensión de alimentación y variabilidad de los componentes, entre otras.

- 2. Es abierta porque toda la información sobre su diseño está gratuitamente disponible en esta web (diagrama esquemático, diseño del circuito impreso, código fuente del firmware y del software, diseño del gabinete), para que sea usada sin restricciones por empresas y profesionales en sus productos y procesos productivos, sin que sea necesario notificar en forma alguna sobre su uso, y pudiendo cada uno modificar libremente el diseño publicado para adaptarlo a sus propias necesidades.

- 3. Es argentina porque es una plataforma desarrollada por PyMEs, profesionales y docentes, sin recurrir al aporte directo del estado o de corporaciones multinacionales, lo que permite ofrecer versiones basadas en distintos procesadores, a partir del uso combinado de capas de abstracción de hardware (HAL) y de una interfaz de programación de aplicaciones (API) pensadas para su uso conjunto con un sistema operativo de tiempo real, siguiendo una estructura de funciones tipo POSIX.

La CIAA cambia la lógica con la cual se agrega valor a la producción industrial porque rompe un esquema individual donde cada empresa debe afrontar en soledad todos los costos, riesgos e incertidumbres que conlleva el desarrollo de nueva tecnología, y lo reemplaza por otro colaborativo en el que muchos de esos riesgos y costos se minimizan o incluso desaparecen gracias a esta nueva forma de construir conocimiento.

Estas características disruptivas y distintivas no sólo permiten incorporar tecnología electrónica para hacer más competitiva a la industria, sino que además empodera al empresario PyME y a los desarrolladores independientes al permitirles diseñar sistemas a la medida de sus necesidades sin depender de empresas multinacionales que ofrecen soluciones propietarias cerradas, que son complejas de escalar.

### A3.2- Requerimientos del proyecto

A continuación se describirán solamente los requerimientos iniciales asociados al Hardware, mas información sobre el resto de los requerimientos se pueden encontrar en el documento "Propuesta para el desarrollo de una Computadora Industrial Abierta Argentina" [11].

### A3.2.1- Requerimientos iniciales de hardware.

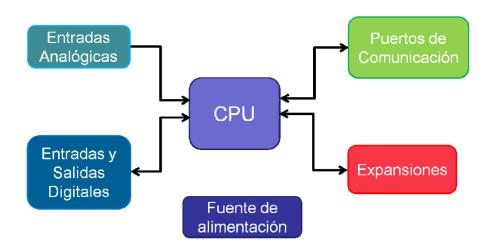

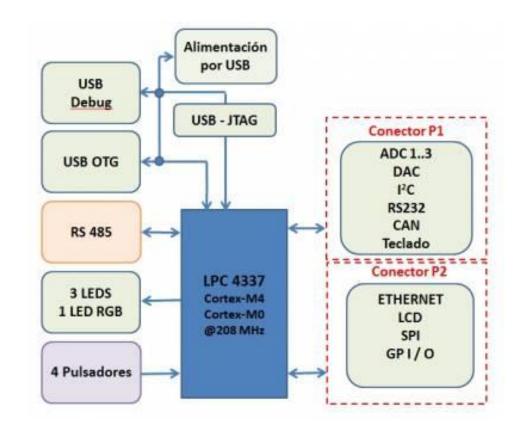

El hardware comprende los componentes físicos de la computadora industrial, dispositivos electrónicos, características eléctricas e interfaces de comunicación. A grandes rasgos, se agrupan dichas características en el diagrama de la Figura N°A3-1.

Figura N°A3-1. Diagrama general del hardware propuesto para la plataforma

La CIAA contará con las siguientes características generales de hardware:

- Fuente de alimentación con voltaje de entrada de 24 V (CC)

- Unidad central de procesamiento: Microcontrolador basado en ARM Cortex-M4F o equivalente

- Entradas digitales con rango 2-30 V (CC)

- Entradas analógicas tipo Voltaje (0-10 V) y Lazo de Corriente (4-20 mA)

- Salidas digitales a relé (NA/NC) y open-drain

- Interfaces de comunicación:

- o Ethernet

- o RS-232

- o RS-485

- Bus para conexión de módulos extra tipo RS-422

### A3.2.2 - Requerimientos finales de hardware

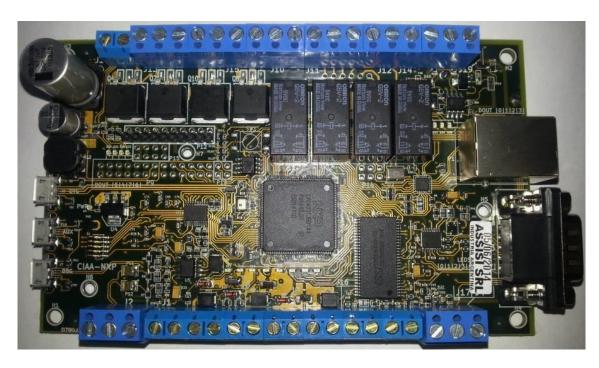

A las antes mencionados requerimientos se le fueron agregando algunos otros que dieron como base el desarrollo de la CIAA- NXP [12], Figura N°A3-2. Uno de ellos muy importante a destacar es que la plataforma desarrollada debía ser realizada con un microcontrolador cuyo encapsulado no fura BGA (Ball Grid Array).

Casi al mismo tiempo que se comenzó con el desarrollo de la plataforma basada en el microcontrolador de la firma NXP, se comenzó con el desarrollo de una plataforma similar basada en un microcontrolador de Freescale [13], Figura N°A3-3.

Actualmente se están desarrollando otras plataformas basadas en microcontroladores de Microchip, ST (CIAA- Safety) e inclusive en micropocesadores y FPGA como ser la CIAA –INTEL y la CIAA- ACC).

Figura N°A3-2. Diseño de plataforma CIAA-NXP.

N°A3-3. Diseño de plataforma CIAA-FSL.

Figura

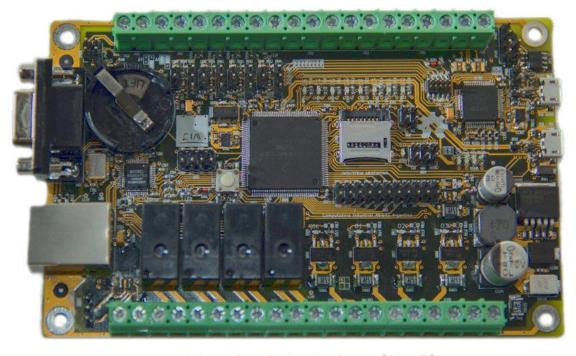

### A3.3 - EDU- CIAA

Con el objetivo de abaratar costos y reducir su complejidad de la CIAA-NXP se desarrollo la EDU-CIAA-NXP, la cual incorpora sólo algunas de las funcionalidades de la CIAA-NXP.

A su vez, con el fin de permitir el desarrollo de algunas prácticas sencillas sin que sea necesario recurrir a hardware adicional, incluye además algunos recursos que no están presentes en la CIAA [14], la Figura N°A3-4 nos muestra el diagrama en bloques de dicha plataforma, mientras la Figura N°A3-5 podemos verla físicamente.

Figura N°A3-4. Diagrama de bloques de la EDU-CIAA-NXP.

Figura N°A3-5. Diseño de plataforma EDU-CIAA-NXP.

### A3.4 - EDU-CIAA-FSL

Dicha plataforma, al momento de comenzar el trabajo del grupo, se encontraba en desarrollo, donde los participantes eran:

- Eduardo Filomena UNRE

- Gonzalo Cuenca UNRE

Quienes habían sido los encargados del diseño de la EDU-CIAA-NXP [15].

### Anexo IV Selección del Software de PCBs

### A4- Selección del software de PCBs

Existen numerosas alternativas a considerar al momento de seleccionar el software (EDA tool) para el diseño de circuitos impresos de electrónica. En este documento mencionaremos las alternativas consideradas y la selección realizada. A continuación se detallan los criterios de selección considerados.

### A4.1- Consideraciones

A continuación se enumeran las consideraciones que se tuvieron en cuenta al momento de seleccionar el software de diseño.

- Licencia de software

- Sistemas operativos soportados

- Características técnicas

- Experiencia previa

### A4.1.1- Licencia de software

Se evaluó la licencia de cada software de diseño de PCB. A diferencia de una empresa, donde generalmente solamente una o dos personas son las encargadas de realizar el diseño final de un PCB, cuando se trata de grupos de trabajo el costo de la licencia de software es un factor muy importante. En un grupo de trabajo como el propuesto en este proyecto se inicia con 4 personas que pueden trabajar en forma concurrente, dentro de la UNLaM, cada una en un puesto de trabajo, o en sus respectivos hogares. Además se planea un crecimiento de este grupo.

Existen alternativas de software para diseño de circuitos impresos con licencia de software libre y Open Source. Este tipo de licencias son las más beneficiosas en un grupo de trabajo conformado dentro de la universidad debido a que ofrece numerosos beneficios:

- Se puede obtener el software y utilizarlo sin costo.

- Se puede instalar en todas las estaciones de trabajo que se desee.

- Se puede usar en proyectos comerciales con fines de lucro.

- Se puede estudiar el funcionamiento interno del programa.

- Con conocimientos de programación se puede modificar o adaptar el programa para algún propósito específico o a medida.

- Se puede ofrecer el software a los alumnos o participantes para que lo instalen en sus hogares.

### A4.1.2- Sistemas operativos soportados

Es importante también, a la hora de seleccionar un software, tener en cuenta el sistema operativo sobre el cual debe ejecutarse. Si bien es verdad que en la gran mayoría de los ambientes de trabajo se utiliza el sistema operativo Windows (Microsoft), existen muchos usuarios avanzados que utilizan sistemas operativos GNU/Linux (Ubuntu/Debian) o Mac OS X (Apple) para el trabajo cotidiano. Por lo tanto se toma como uno de los criterios de selección que el software de diseño tenga soporte para por lo menos dos sistemas operativos:

- Sistemas operativos Windows.

- Sistemas operativos GNU/Linux (Ubuntu o Debian).

### A4.1.3- Características técnicas

Al momento de analizar un software para PCB son muchas las características técnicas a analizar, y cada software en particular es una tarea compleja. Como algunas de las características mínimas generales podemos establecer las siguientes:

- Debe poseer captura de esquemático.

- Debe poseer edición de PCB.

- Se debe poder agregar y editar elementos de bibliotecas de símbolos esquemáticos y footprints.

- Debe permitir diseños multicapa.

- Debe poder generar e inspeccionar archivos gerbers.

En esta etapa inicial se analiza esta selección solo para diseños por debajo de 1 GHz, sin embargo se tiene preferencia por aquel software que presente ruteo de pares diferenciales y control exacto de longitud de pista.

Al momento de seleccionar un software se buscarán diseños ya realizados con el mismo como prueba de sus características técnicas y su grado de complejidad.

### A4.1.4- Experiencia previa

Al momento de seleccionar un software para diseño de PCB se considerará como un factor relevante la experiencia previa que posean los alumnos y docentes.

### A4.2- Software disponible para el diseño de circuitos impresos

En la Tabla N°A4-1 se puede ver los programas más importantes para el diseño de PCB y sus principales características [5].

Tabla N°A4-1. Programas de diseño de PCB.

| Programa | Licencia                                                    | Comentarios                                                    | URL                                                 |

|----------|-------------------------------------------------------------|----------------------------------------------------------------|-----------------------------------------------------|

| Altium   | Paga<br>(aprox.<br>1.000 a<br>5.500<br>USD por<br>estación) | Es uno de los más conocidos y empleados en la industria local. | http://www.altium.com/                              |

| AutoTrax | Paga (47<br>USD)                                            | Simple de usar.<br>Muy conocido.                               | http://kov.com/                                     |

| Eagle    | Paga (<br>aprox<br>300 USD<br>por<br>usuario)               | GNU/Linux y<br>Windows.                                        | http://www.cadsoftusa.com/                          |

| CADSTAR  | Costo<br>elevado                                            | No es muy<br>utilizado en la<br>región.                        | http://www.zuken.com/en/products/pcb-design/cr-8000 |

| KICAD    | GPL.<br>Gratuito                                            | Es el más conocido en el software libre                        | http://kicad-pcb.org/                               |

| Programa           | Licencia                                | Comentarios                                                                                                                                                          | URL                            |

|--------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

|                    |                                         | y evoluciona constantemente.                                                                                                                                         |                                |

| Fritzing           | GPL.<br>Gratuito                        | Está pensado para diseños simples de hobistas.                                                                                                                       | http://fritzing.org/           |

| FreePCB            | GPL.<br>Gratuito                        | Interfaz amigable. No ha evolucionado desde 2011.                                                                                                                    | http://www.freepcb.com/        |

| Geda (gschen, pcb) | GPL.<br>Gratuito                        | Capacidades<br>básicas. El editor<br>de PCBs no ha<br>evolucionado en<br>los últimos años.                                                                           | http://www.geda-project.org/   |

| PADS de Mentor     | Más de<br>15.000<br>USD por<br>usuario. | Alternativa muy costosa para grupos de trabajo. De difícil acceso para pymes, estudiantes y emprendedores.                                                           | http://www.mentor.com/pcb/pads |

| Allegro de Cadence | Más de<br>24.000<br>USD por<br>usuario. | Posee muchos módulos adicionales que suman al costo base. Alternativa muy costosa para grupos de trabajo. De difícil acceso para pymes, estudiantes y emprendedores. | http://www.cadence.com/        |

| Orcad de Cadence   | Más de<br>6.500<br>USD por<br>usuario   | Alternativa muy costosa para grupos de trabajo. De difícil acceso para pymes, estudiantes y emprendedores.                                                           | http://www.orcad.com/          |

### A4.3- Preselección

Analizando las alternativas, y considerando los criterios de selección de software expuestos anteriormente, se realiza una pre-selección de las siguientes alternativas:

- Altium

- Eagle

- Kicad

Los demás se descartan por ser de alto costo para el caso de aquellos que están por encima de los 1.000 USD, por ser de poco uso local, o por no haber evolucionado lo suficiente en los últimos años para el caso de los gratuitos o de software libre.

### A4.3.1-Ventajas y Desventajas

La Tabla N°A4-2 presenta las ventajas y desventajas de cada una de las alternativas preseleccionadas.

Tabla N°A4-2. Ventajas y desventajas de los software preseleccionados.

| Altium                                                                                                |                                                                                                                 |  |  |  |  |

|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Ventajas                                                                                              | Desventajas                                                                                                     |  |  |  |  |

| Es muy usado en la industria local.                                                                   | Posee licencia paga.                                                                                            |  |  |  |  |

| Posee capacidades de integridad de señal (5.500 USD).                                                 | Solo para estaciones Windows.                                                                                   |  |  |  |  |

| KICAD                                                                                                 |                                                                                                                 |  |  |  |  |

| Ventajas                                                                                              | Desventajas                                                                                                     |  |  |  |  |

| Experiencia previa de alumnos Taller de electrónica desde 2007.                                       | Poco conocido en la industria.                                                                                  |  |  |  |  |

| Experiencia previa en otras materias (Tecnología y Robótica).                                         | Interfaz y formatos cambiantes debido a su veloz evolución.                                                     |  |  |  |  |